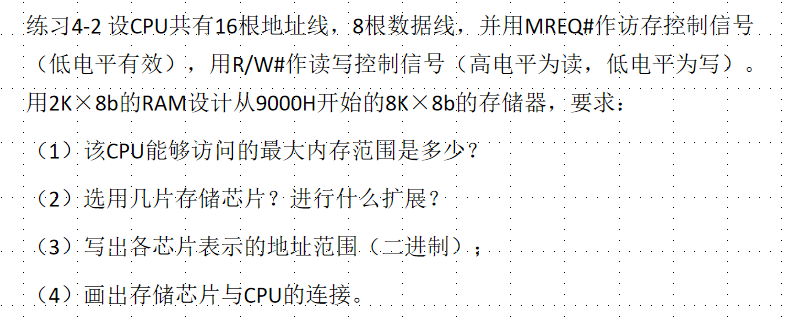

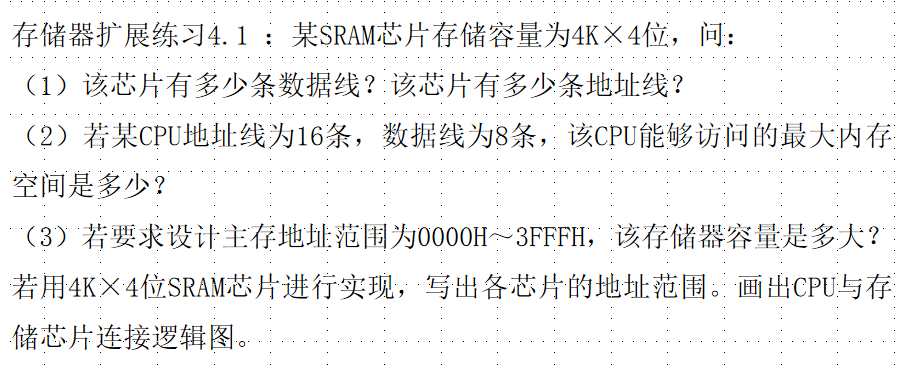

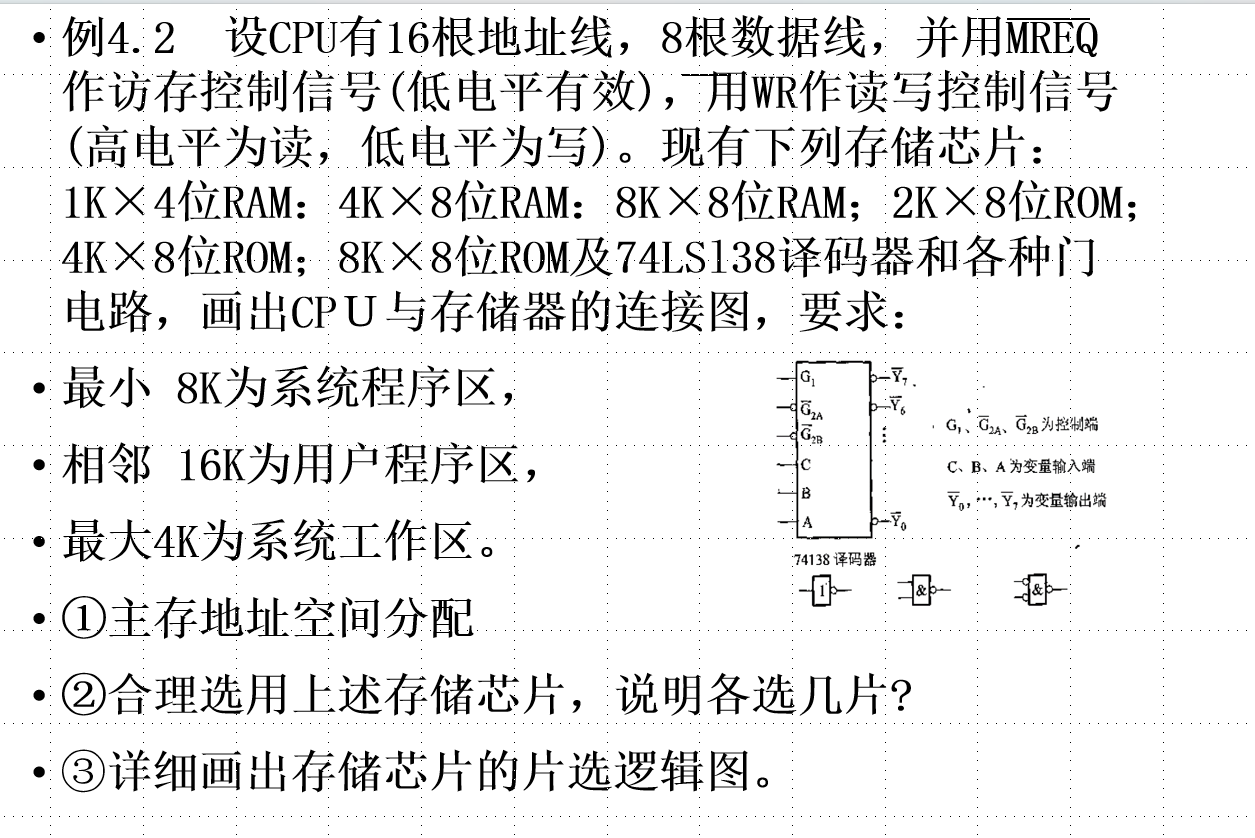

专题四:存储器扩展设计题

这一专题的基础知识见主存储器

对于一个存储器芯片来说,宏观上是有地址线引脚(eg

当然其中片选信号又CS和CE两种

读写信号可能是一个引脚或者是两个引脚

像如上面的芯片的大小就是1K * 4位

然而很多时候我们需要对存储器扩展,扩展有三种,字扩展,位扩展,字位同时扩展

一般算用多少片芯片的时候会采用这个公式,这个公式一定要写在试卷上

前面的4代表字扩展用4片 后面的2代表位扩展用2片

也就是要用8片 1K 4b的芯片,两个芯片作为一组 共四组 来构成4K 8b的芯片

一般我们的考题中:

开始地址 末地址 容量 是已知其二求另一个的 这就派生出三种题目来

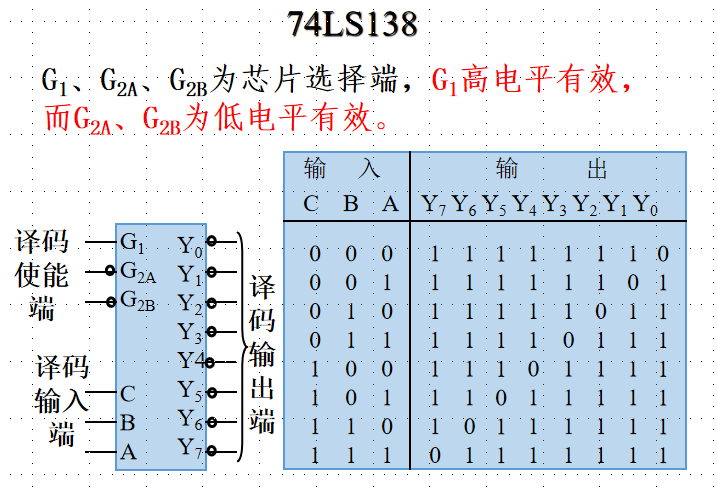

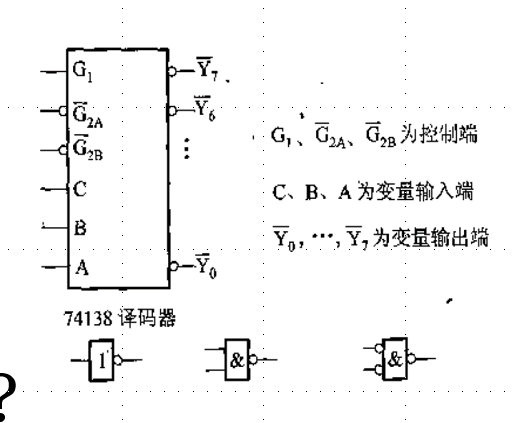

一般我们的题目都会用38译码器

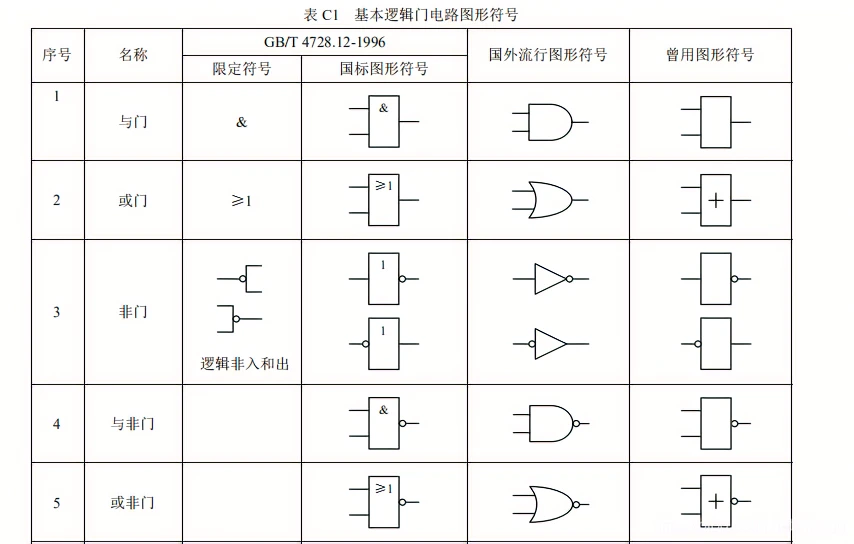

还要了解一些常见的门

| 逻辑运算 | 运算规则 |

|---|---|

| 与 | 有 0 为 0,全 1 为 1 |

| 或 | 有 1 为 1,全 0 为 0 |

| 非 | 1 为 0,0 为 1 |

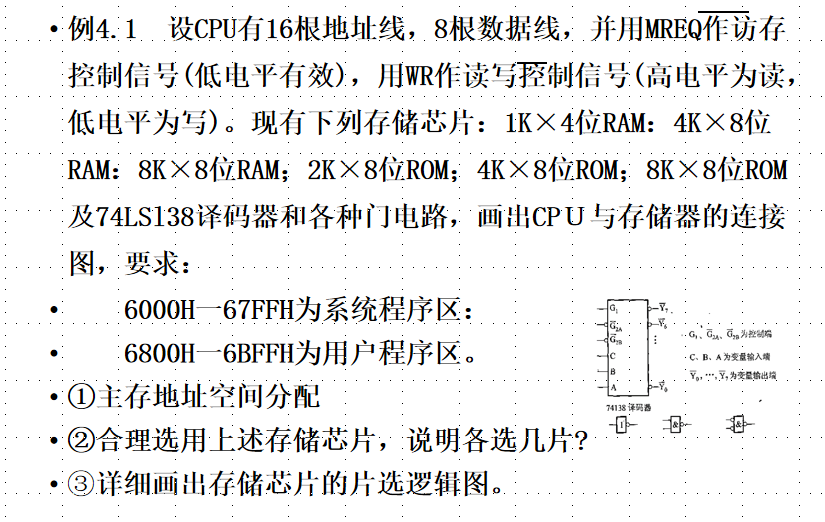

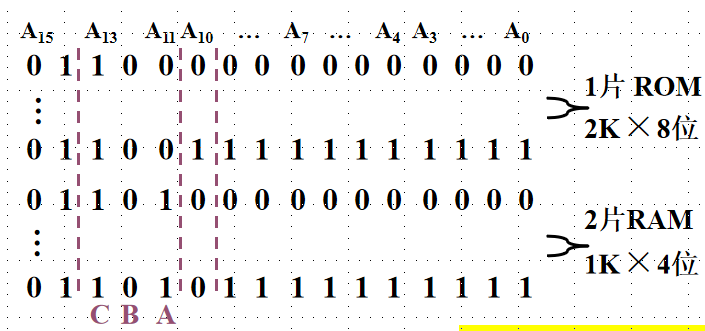

做这种题的第一步就是先把给出的地址写成二进制的形式

这里要记得在上面标

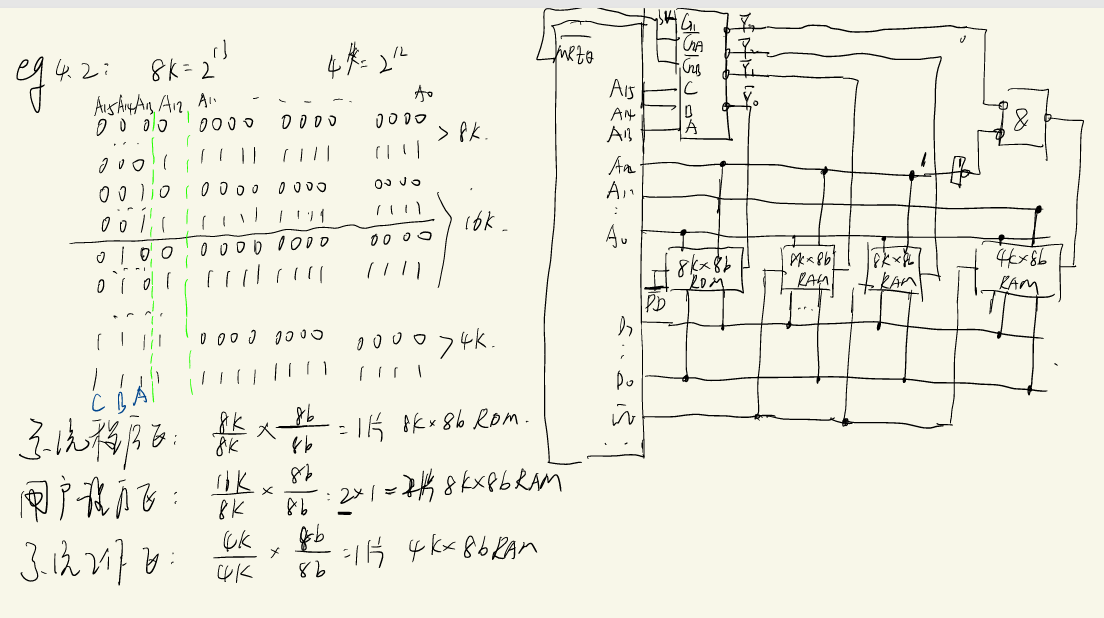

系统程序区:

0110 0000 0000 0000

……

0110 0111 1111 1111

用户程序区:

0110 1000 0000 0000

……

0110 1011 1111 1111

根据二进制地址或者是容量 知其二算其一

在这个题中,系统程序区从低11位全为0 变为低11位全为1

容量:11位-----

用户程序区从低10位全为0 变成了低10位全为1

容量:1K * 8

第二步确定芯片的数量以及类型

对于系统程序区:不希望能够修改:采用ROM(只读) 正好有合适的2K * 8的

对于用户程序区:使用RAM,没有合适的只能通过扩展的方式,选择的原则是能使用的芯片越少越好 这里选择使用1K * 4的芯片进行扩展:

使用片数:

使用两片进行位扩展

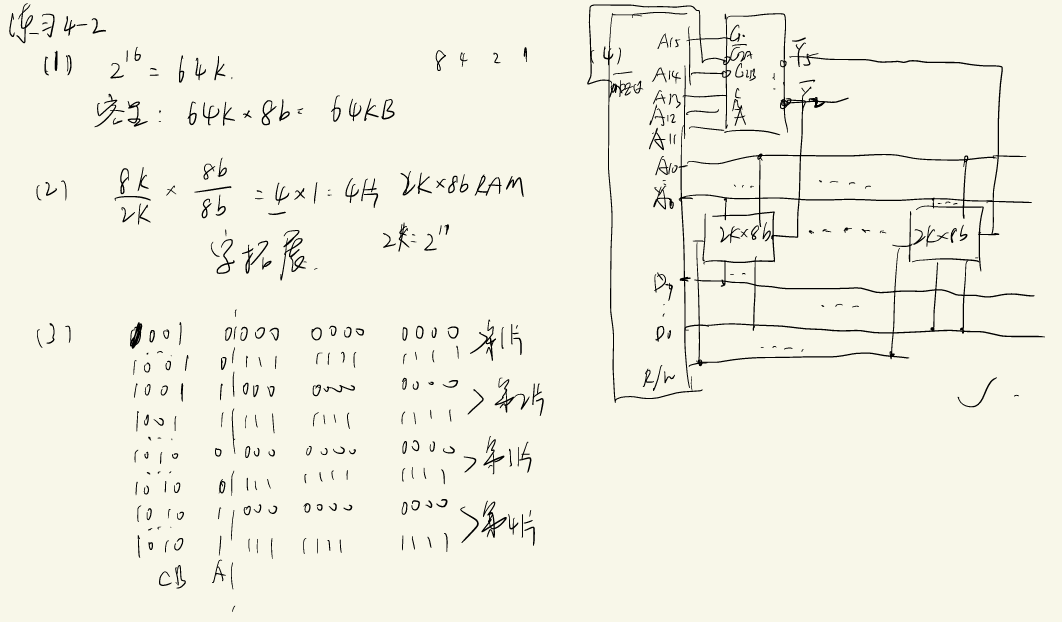

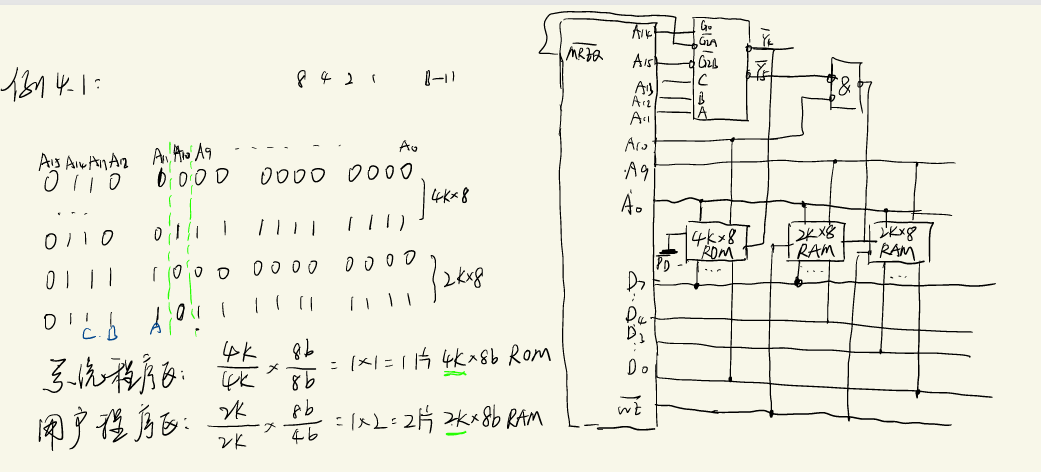

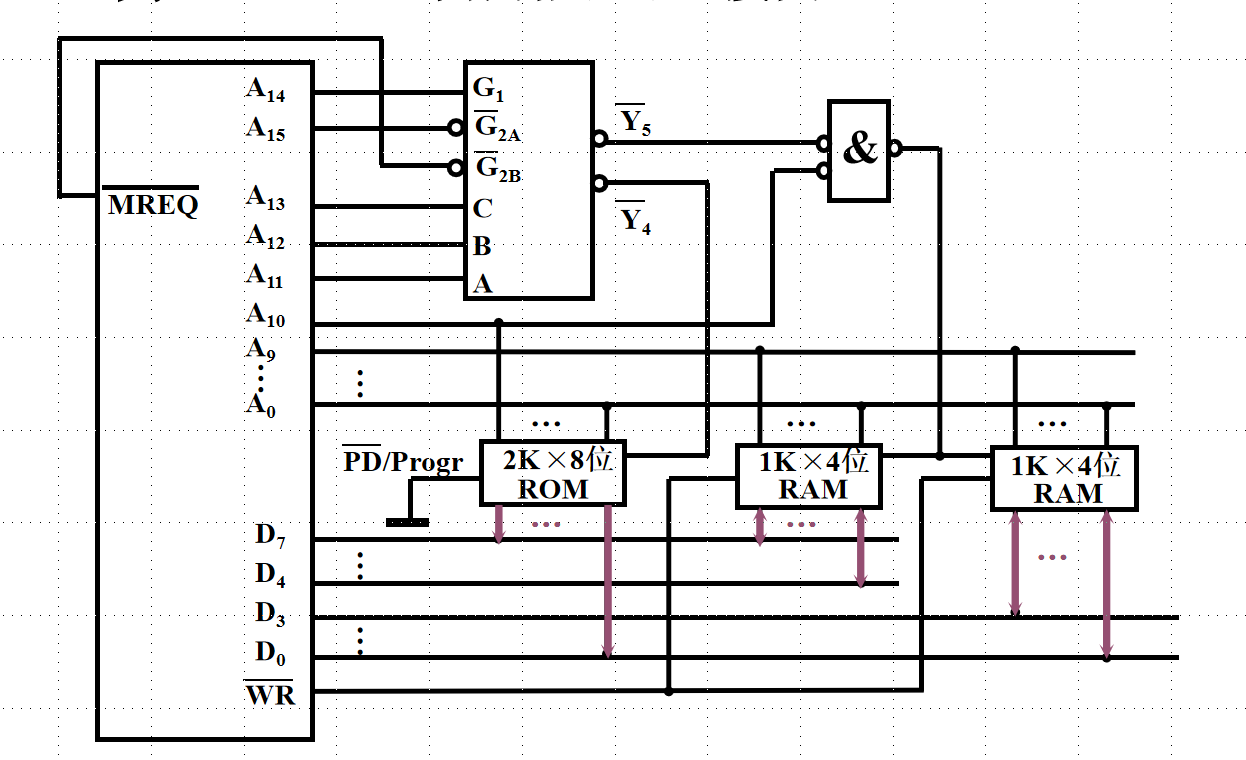

第三步是分配地址线

与芯片连接的地址线看的是芯片的大小!

每一个芯片的地址引脚直接和CPU的低位地址相连接就行

第四步是确定片选信号:

剩下的就是与38译码器顺势连接

一般是在最大值(最左边的线)在往上取3跟线分别作为CBA(A在右边),然后就能根据二进制得到译码之后的片选的那个编码了

再高位就根据1和0与G1 G2A G2B顺势相连就可以 一定不要忘了MREQ

但是值得注意的是,A10 RAM没用到 也应该作为片选信号连进去 这就涉及到了常见的门电路,注意都是低电平有效哈 适当用取反

但我没想明白G2A和G2B明明都是低电平有效 A15和MREQ也刚好都是0 为什么还加了取反的符号??

**画图的时候:

假设

4片是说要用4片2K * 8b的芯片 也就是说画4个芯片(多的话中间可以省略)

第二个2是位扩展----说明两个芯片要绑定变为1组------图中体现的是地址线上连接的不同

第一个2是字扩展----说明这样的组有2组------在写地址的时候要写2组----每组全0变成全1的个数跟原来芯片的大小有关系 (因为地址线接入的是里面的每个小的芯片)

先用那个2K * 8 取决于ABC(最高顺势往高位找3位)来选那一组2K * 8

如果多组的大小不一样,会有在一组用到了 在另一组用不到的地址线,这个时候需要用门电路进行组合**

整体步骤:

这个图画错了哈哈哈好像

注意MREQ 和 PD/Progr

必要的时候可以给G1 G2A G2B进行接高电平(3V)或者接地

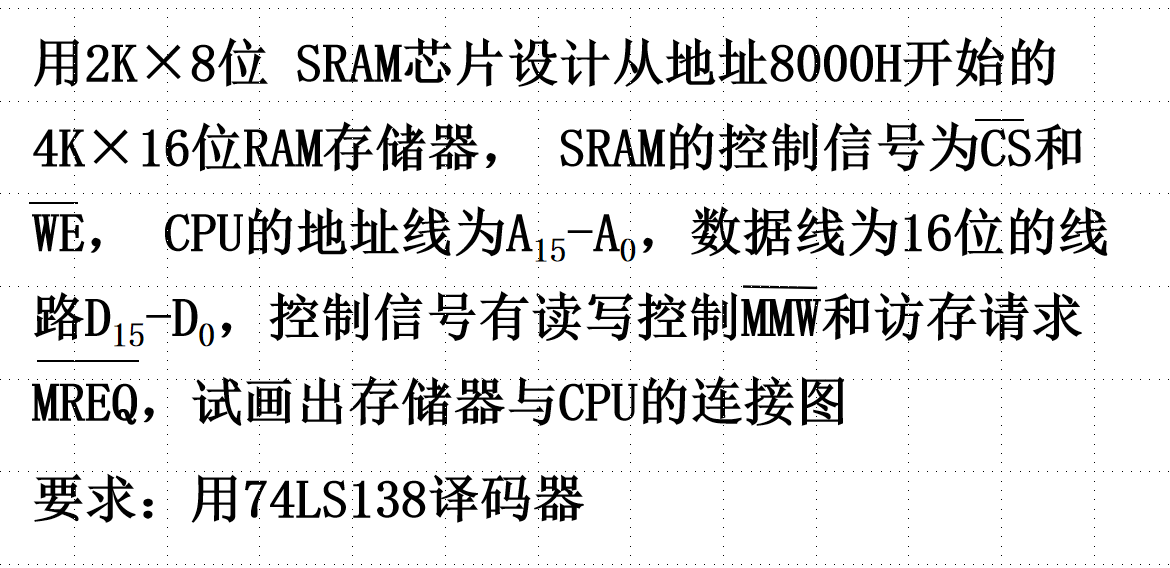

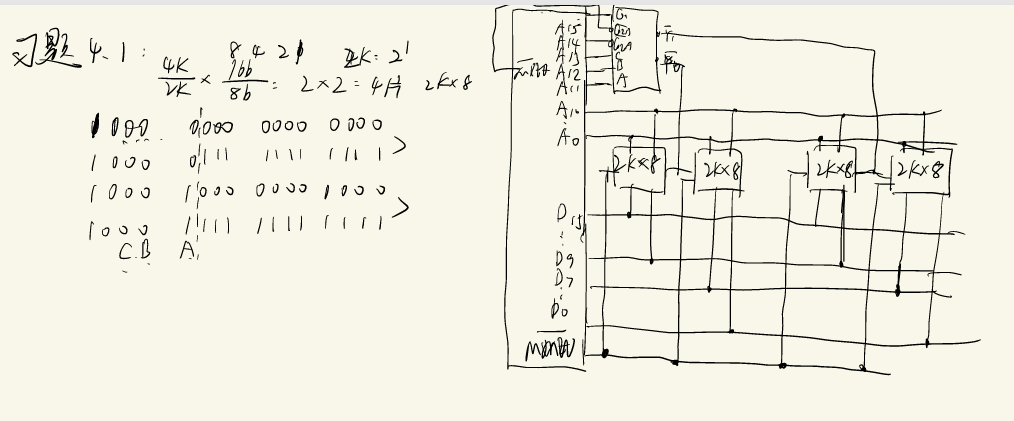

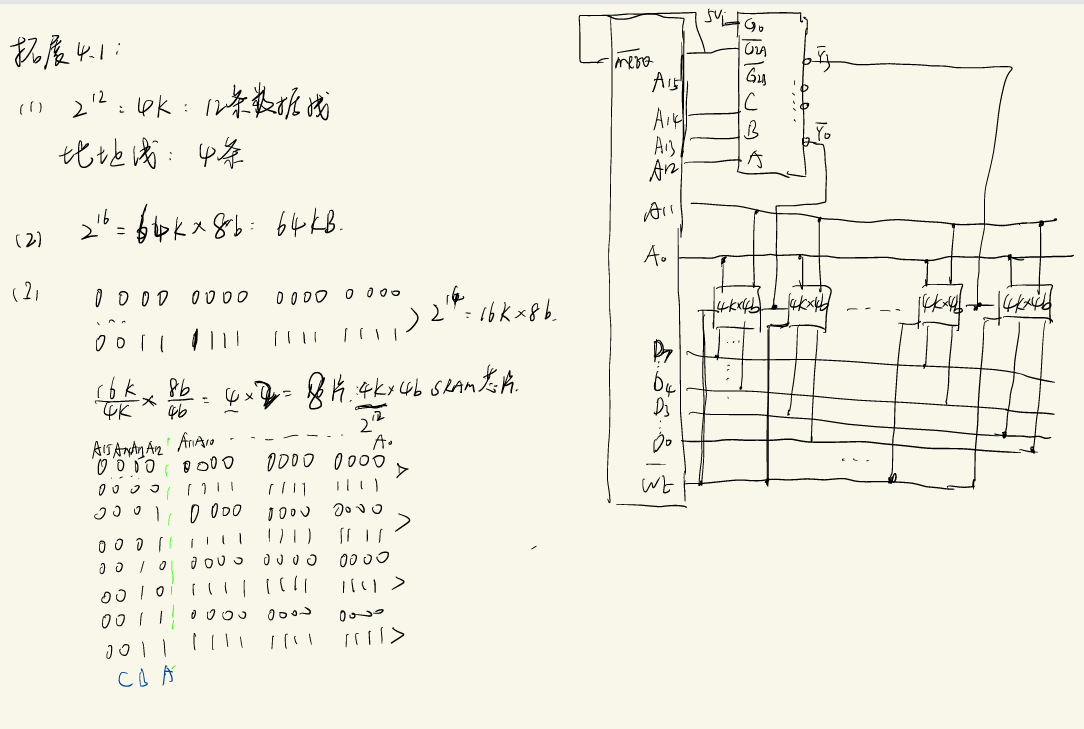

习题4.1: